2<sup>nd</sup> IEEE International Workshop on Advanced Information Systems for Enterprises (IWAISE'12)

# Modeling of Architectural Reconfiguration Case Study: Automated Teller Machine

Taha Abdelmoutaleb Cherfia

in collaboration with

Dr. Faïza Belala and Nadira Benlahrache

LIRE laboratory, University Mentouri Constantine

# Outline

- Introduction

- Related Work

- Basic Concepts

- Bigraphical Reactive System (BRS)

- Architecture Analysis and Design Language (AADL)

- Approach

- Case study: ATM System

- Conclusion & Future Work

#### Introduction

- Rapidly growing complexity of software systems.

- Software Architecture, a key approach to decrease complexity.

- Architecture Description Languages, a representation in terms of components, connectors and configuration.

- ADLs facilitate the high-quality development of software systems.

- Only few ADLs are provided with some hold for the dynamic behavior.

#### Introduction

- AADL, an international standard to model both structural and behavioral aspects of SA.

- The lack of a concrete formal model to define AADL semantics.

- An extended BRS-based approach to formalize the dynamic architectural reconfiguration.

# Related Work

- R. Allen, R. Douence, and D. Garlan, "Specifying and analyzing dynamic software architectures"

- Clear separation between individual components behavior and software architectural dynamics.

- L. Baresi, and R. Heckel, "*Tutorial introduction to graph transformation: A Software Engineering Perspective*"

- Class diagram to represent a software architecture.

- Z. Chang, X. Mao, and Z. Qi, "Towards a formal model for reconfigurable software architectures by bigraphs"

- Graph transformation to only define structural reconfiguration.

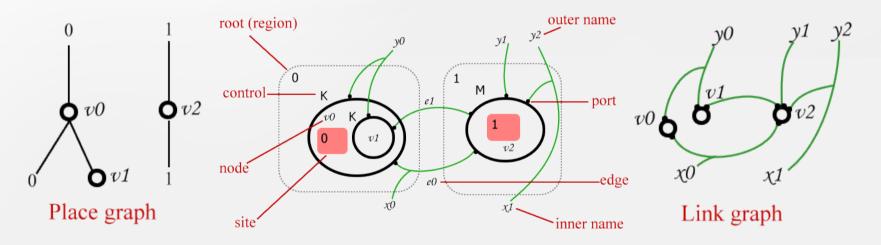

- Bigraphical Reactive System is a graphical model.

- Emphases both locality and connectivity of distributed systems.

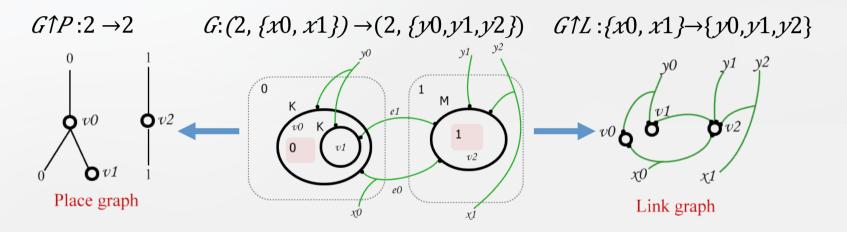

Bigraph consists of two graphs :

Place graph: physical location of nodes.

Link graph : interaction between these nodes.

- Formally a bigraph takes the form:  $G=(V, E, ctrl, G^{\uparrow}P, G^{\uparrow}L): I \rightarrow J$

- V is a finite set of nodes.

- *E* is a finite set of edges.

- $ctrl = V \rightarrow K$  is a control map.

Signature

•  $GTP = (V, ctrl, prnt): m \rightarrow n$  is the place graph

- $prnt: m \not \downarrow \uparrow @ V \rightarrow V \not \downarrow \uparrow @ n$  is the acyclic parent map.

- *m* is a finite ordinal number which represents sites.

- *n* is a finite ordinal number which represents regions.

• Formally a bigraph takes the form:  $G=(V, E, ctrl, G^{\uparrow}P, G^{\uparrow}L): I \rightarrow J$

- $G^{\uparrow}L = (V, E, ctrl, link): X \rightarrow Y$  is the link graph

- $link: X \Downarrow \uparrow @ P \rightarrow E \Downarrow \uparrow @ Y$  is the link map.

- *X* represents the inner names.

- *Y* represents the outer names.

- *P* is a set of ports.

- I = (m, X) represents the inner face.

- $J = \langle n, Y \rangle$  represents the outer face.

#### Example :

- *V*={*v*0, *v*1, *v*2}

- $E = \{e0, e1\}$

- $K = \{ \nu 0:2, \nu 1:2, \nu 2:4 \}$

- $prnt = \{ v0: \emptyset, v1: v0, v2: \emptyset \}$

- I=(2, {x0, x1})

- *J*=(2, {*y*0,*y*1,*y*2})

7

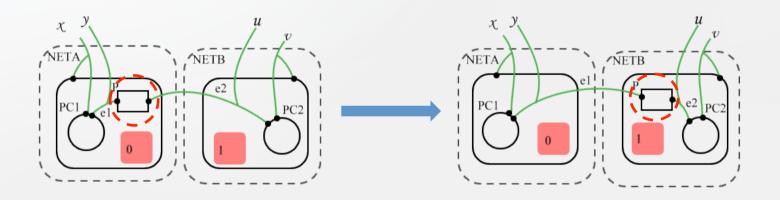

- BRS consists of a category of bigraphs and a set of reaction rules.

- Reaction rules define the dynamics of bigraphs :

- Nesting

- Linkage

- A reaction rule (*R*, *R'*, η) consists of a redex (*R*:*m*→*f*) which may be transformed to a reactum (*R1'* :*m1'* → *f*) to rewrite the bigraph where η: *m1'* → *m* is map of ordinals.

#### Example :

- Redex :  $R: 2 \rightarrow (2, \{x, y, u, v\})$

- Reactum : R1' :  $2 \rightarrow (2, \{x, y, u, v\})$

- Map : η:{2→2}

- Transformation : locality reconfiguration

# Basic Concepts : AADL

- Architecture Analysis and Design Language is an international standard.

- Represents a real-time embedded system as a componentbased architecture.

Software : data, process, thread, thread group and subprogram.

Platform : processor, memory, device and bus.

Composite : system.

- Models the interaction of the software components and their target platforms.

- Represents operational modes to describe the dynamic behavior of systems.

- BRS, a suitable platform to formalize the installation activity of AADL systems.

- Formal mapping based on correspondences between AADL and bigraph elements.

| AADL elements            | Bigraphical semantic                                                                                                                                                            |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System: <i>S</i>         | Bigraph/Region:<br>$S = (V \downarrow S, E \downarrow S, ctrl \downarrow S, G \downarrow S \uparrow P, G \downarrow S \uparrow L): I \downarrow S \rightarrow J \downarrow S$   |

| Component: C             | Node $C \in V \downarrow S$                                                                                                                                                     |

| Port/Role: P             | Port/Inner-name or Outer-name: $P \in I \downarrow S \cup J \downarrow S$                                                                                                       |

| Interaction Port-Role: L | Hyper-edges: $L \in E \downarrow S$                                                                                                                                             |

| Hierarchy                | Imbrication of Nodes and Sites: $prnt \downarrow S : m \downarrow S \cup V \downarrow S \rightarrow V \downarrow S \cup n \downarrow S$                                         |

| Binding properties       | Composition: $S \downarrow S^{\circ} S \downarrow H$ where<br>$S \downarrow S$ and $S \downarrow H$ are bigraphs modeling respectively both<br>software and hardware parts of S |

• Enrich the proposed mapping rules set between AADL and bigraph concepts :

✓ Extend the control function to deal with all possible modes.

✓ Exploit the bigraphs reaction rules.

• Dynamic runtime formalization :

| AADL elements            | Bigraphical semantic                                                                                                                                     |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configuration <i>S↓m</i> | Bigraph: $S \downarrow m = (V \downarrow S, E \downarrow S \uparrow m, ctrl \uparrow m, G \downarrow S \uparrow P, G \downarrow S \uparrow L \uparrow')$ |

| Mode transitions         | Reaction rule: $\mathcal{R}=(R\downarrow m, R\downarrow m'\uparrow', \eta)$                                                                              |

• A bigraph Slm over a signature Klm is given by:

$S\downarrow m = (V\downarrow S, E\downarrow S\uparrow m, ctrl\uparrow m, G\downarrow S\uparrow P, G\downarrow S\uparrow L\uparrow')$  where:

- $m \in \mathcal{M}$  represents a current operational mode.

- $\mathcal{M}$  is a finite set of modes.

- $\mathcal{K}\uparrow m = \mathcal{K}\cup\mathcal{M}$  is an extended signature.

- K(C) = (arity(C), m) is an extended control function.

- $ctrl \uparrow m: V \downarrow S \rightarrow K \uparrow m$  is a new control map assigning to each node *C* a control  $K \in K \uparrow m$

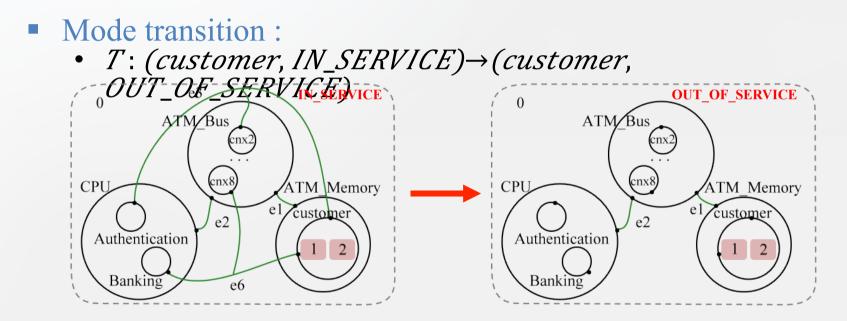

- $T:(C, m) \rightarrow (C, m')$  is a mode transition of a component *C* between *m* and *m'*.

- Formally *T*: *R*=(*R*↓*m*, *R*↓*m*' 1', η) is a parametric reaction rule where:

□ *R↓m* is a redex bigraph of a component *C* in a mode *m*.

□ *R'↓m'* is a reactum bigraph of a component *C* in a new mode *m'*.

$\Box \eta$  is a map of ordinals.

- Automated Teller Machine (ATM) is a computerized machine.

- Provides bank costumers with an alternative access to financial transactions.

- An ATM machine consists of :

- Card reader

- Keypad

- Processor

- Modem

- Monitor

- Printer

- Cash dispenser

- ATM system is an embedded real-time system which provides banking services :

- Withdraw cash

- Make deposits

- Transfer funds

- Balance checking

- Basically, an AADL description of ATM System is a collection of interconnected software and hardware components.

| Automated Teller Machine                                                                                                                                                                                                                                                                                                          | Connections                                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| system ATM_System<br>end ATM_System;                                                                                                                                                                                                                                                                                              | <pre>cnx1: data port ATM_Modem.status_data -&gt; ATM_Service.ATM_Status; cnx2: event data port customer.Card_Number_out -&gt; session.Card_Number_in;</pre>                                                                  |

| Software components                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                              |

| customer : process Customer.impl;<br>session : process Session.impl;<br>account : process Account.impl;<br>ATM_Service : process ATM_Service.impl;                                                                                                                                                                                | Installation                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                   | Actual_Processor_Binding => reference CPU applies to customer;<br>Actual_Memory_Binding => reference ATM_Memory applies to<br>account;                                                                                       |

| Execution platform components                                                                                                                                                                                                                                                                                                     | Operational modes                                                                                                                                                                                                            |

| CPU : processor ATM_Processor.impl;<br>ATM_Memory : memory ATM_Memory.impl;<br>ATM_Keypad : device ATM_Keypad;<br>ATM_Screen : device ATM_Screen;<br>ATM_Printer : device ATM_Printer;<br>ATM_Modem : device ATM_Modem;<br>Card_Reader : device Card_Reader;<br>Cash_Dispenser : device Cash_Dispenser;<br>ATM_Bus : bus ATM_Bus; | <pre>modes<br/>IN_SERVICE : initial mode;<br/>OUT_OF_SERVICE : mode;<br/> Mode transitions<br/>IN_SERVICE -[ATM_Service.OFFLINE]-&gt; OUT_OF_SERVICE;<br/>OUT_OF_SERVICE -[ATM_service.ONLINE]-&gt; IN_SERVICE;<br/>17</pre> |

Exploitation of the extended BRS-based approach :

- Reaction rule :

- $\mathcal{R}=(R\downarrow IN\_SERVICE, R\downarrow OUT\_OF\_SERVICE\uparrow', \eta)$  where:

- $R \downarrow I N\_SERVICE : 2 \rightarrow (1, \emptyset)$

- $R' \downarrow O\overline{UT}_OF\_SERVICE : 2 \rightarrow (1, \emptyset)$

- $\eta: 2 \rightarrow 2$

• Signature:

% State of the second sec

- *M*={*IN\_SERVICE, OUT\_OF\_SERVICE*} is the set of operational modes.

Linkage transformation

- K(customer)=(2, IN\_SERVICL - arity(customer) = 2

- $m = IN\_SERVICE$

connectivity reconfiguration

•  $K(customer) = (0, OUT_OF\_SERVICE)$ - arity(customer) = 0

# Conclusion & Future Work

- AADL and the absence of a concrete formal model in its standard.

- A new extended BRS-based approach to model the dynamic architectural reconfiguration.

□High-level modeling of software architecture.

• Our ongoing research focuses on handling BRS to adopt the context-aware information.